# xPC Target

## For Use with Real-Time Workshop®

- Modeling

- Simulation

- Implementation

Version 2

#### How to Contact The MathWorks:

www.mathworks.com Web

comp.soft-sys.matlab Newsgroup

support@mathworks.com Technical support

suggest@mathworks.com Product enhancement suggestions

bugs@mathworks.com Bug reports

doc@mathworks.com Documentation error reports

service@mathworks.com Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 Phone

508-647-7001 Fax

The MathWorks, Inc. Mail

3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

xPC Target I/O Reference Guide

© COPYRIGHT 2000 - 2005 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

MATLAB, Simulink, Stateflow, Handle Graphics, Real-Time Workshop, and xPC TargetBox are registered trademarks of The MathWorks, Inc.

Other product or brand names are trademarks or registered trademarks of their respective holders.

| Printing History: | November 2000  | Online only | New for Version 1.1 (Release 12.0)         |

|-------------------|----------------|-------------|--------------------------------------------|

|                   | June 2001      | Online only | Revised for Version 1.2 (Release 12.1)     |

|                   | September 2001 | Online only | Revised for Version 1.3 (Release 12.1+)    |

|                   | July 2002      | Online only | Revised for Version 2 (Release 13)         |

|                   | September 2002 | Online only | Revised for Version 2.0.1 (Release 13)     |

|                   | September 2003 | Online only | Revised for Version 2.0.1 (Release 13 SP1) |

|                   | June 2004      | Online only | Revised for Version 2.5 (Release 14)       |

|                   | August 2004    | Online only | Revised for Version 2.6 (Release 14+)      |

|                   | October 2004   | Online only | Revised for Version 2.6.1 (Release 14SP1)  |

|                   | November 2004  | Online only | Revised for Version 2.7 (Release 14SP1+)   |

|                   | March 2005     | Online only | Revised for Version 2.7.2 (Release 14SP2)  |

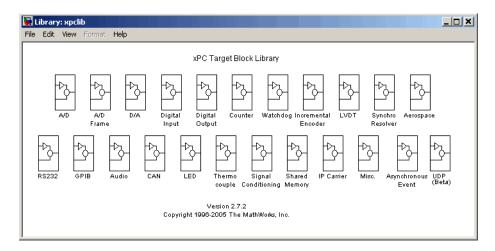

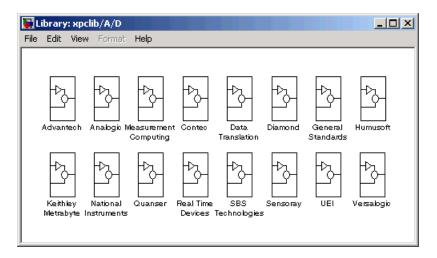

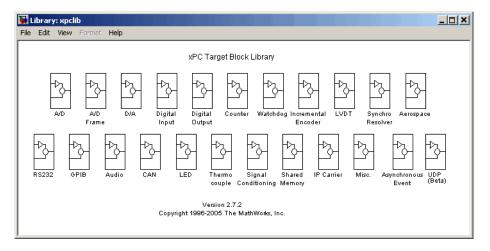

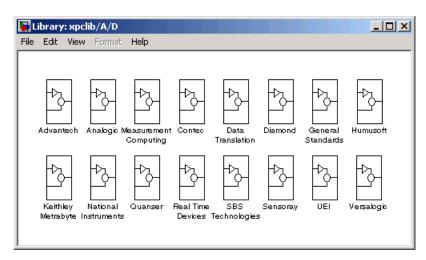

#### xPC Target I/O Library

| VO Driver Blocks                                            | -2          |

|-------------------------------------------------------------|-------------|

| I/O Driver Block Library                                    | -2          |

| Memory-Mapped Devices 1                                     | -5          |

| ISA Bus I/O Devices                                         | -5          |

| PCI Bus I/O Devices                                         | -6          |

| xPC Target I/O Driver Structures 1                          | -7          |

| PWM and FM Driver Block Notes 1                             | -8          |

| Updated Driver Information                                  | 10          |

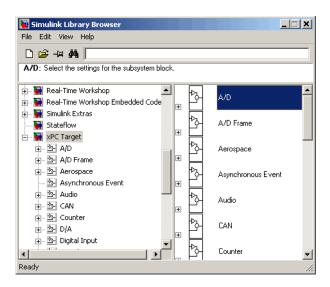

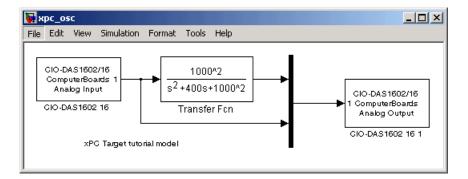

| Adding I/O Blocks with the xPC Target Library 1-1           | 11          |

| Adding I/O Blocks with the Simulink Library Browser 1-1     | 15          |

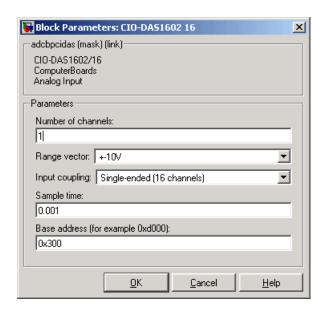

| Defining I/O Block Parameters                               | 19          |

| Serial Communications Suppor                                | rí          |

| Introduction to Serial Drivers 2                            | 2 <b>-2</b> |

| Hardware Connections for RS-232 2                           | -3          |

| Host and Target PC Communication                            | -3          |

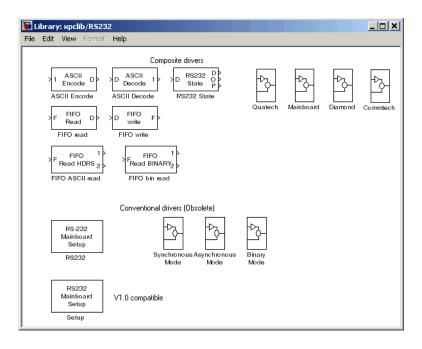

| xPC Target RS-232 and 422/485 Drivers (Composite) 2         | -5          |

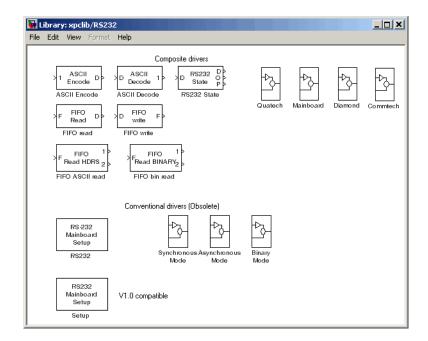

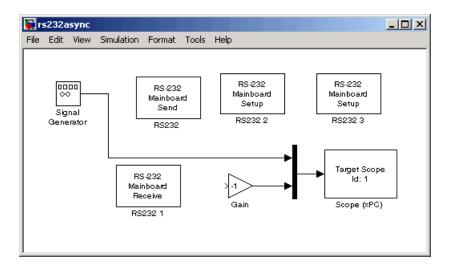

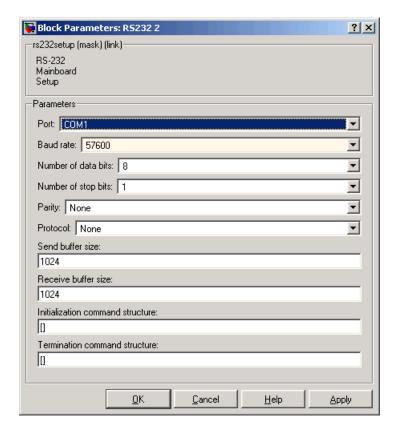

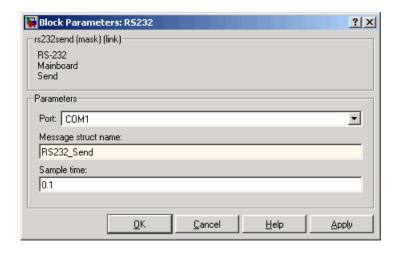

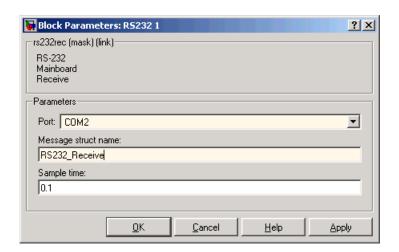

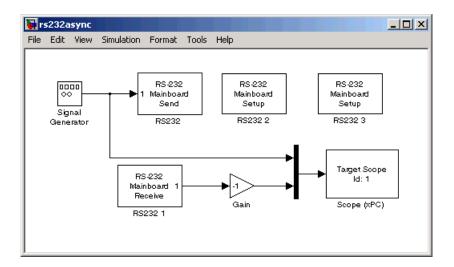

| Adding RS-232 Blocks                                        | -6          |

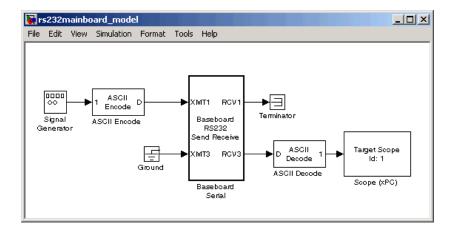

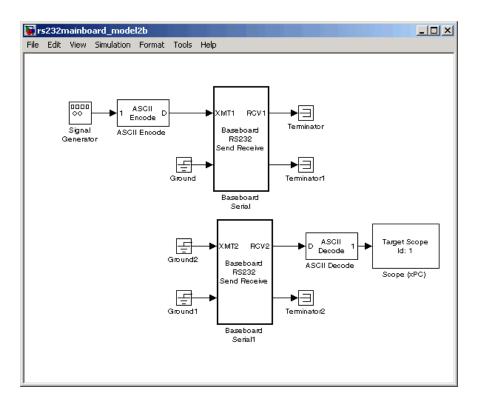

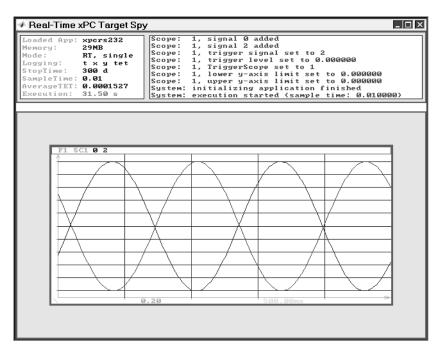

| Building and Running the Target Application (Composite) 2-1 | 11          |

| RS-232/422/485 Simulink Block Reference 2-1                 | 12          |

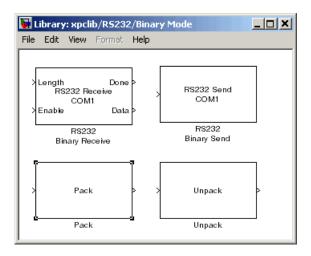

|   | xPC Target RS-232 Drivers (Conventional) Simulink Blocks for RS-232 I/O (Conventional) MATLAB Message Structures for RS-232 I/O (Conventional) RS-232 Synchronous Mode (Conventional) RS-232 Asynchronous Mode (Conventional) RS-232 Simulink Block Reference (Conventional) RS-232 MATLAB Structure Reference (Conventional) RS-232 Binary Mode (Conventional) | 2-60<br>2-61<br>2-62<br>2-71<br>2-83<br>2-88 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2 | GPIB I/O Supp                                                                                                                                                                                                                                                                                                                                                   | ort                                          |

|   |                                                                                                                                                                                                                                                                                                                                                                 |                                              |

|   | Introduction to GPIB Drivers                                                                                                                                                                                                                                                                                                                                    | 3-2                                          |

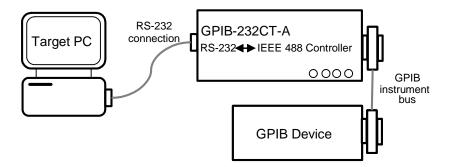

|   | Hardware Connections for GPIB                                                                                                                                                                                                                                                                                                                                   | 3-2                                          |

|   | Simulink Blocks for GPIB                                                                                                                                                                                                                                                                                                                                        | 3-3                                          |

|   | MATLAB Message Structures for GPIB                                                                                                                                                                                                                                                                                                                              | 3-3                                          |

|   | Using GPIB Drivers                                                                                                                                                                                                                                                                                                                                              | 3-5                                          |

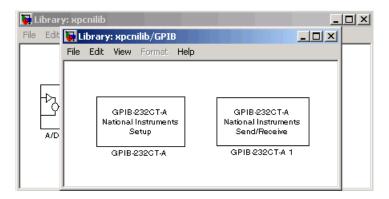

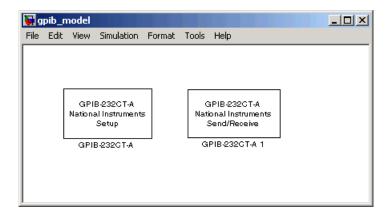

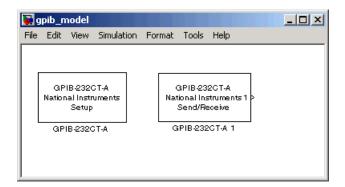

|   | Adding GPIB Driver Blocks                                                                                                                                                                                                                                                                                                                                       | 3-5                                          |

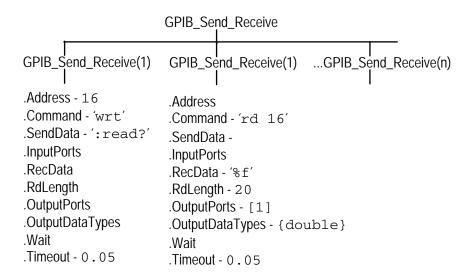

|   | Creating GPIB Message Structures                                                                                                                                                                                                                                                                                                                                | 3-10                                         |

|   | GPIB Simulink Block Reference                                                                                                                                                                                                                                                                                                                                   | 3-13                                         |

|   | GPIB-232CT-A Setup Block                                                                                                                                                                                                                                                                                                                                        | 3-13                                         |

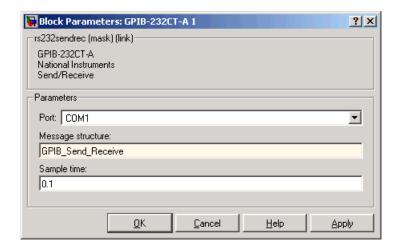

|   | GPIB-232CT-A Send/Receive Block                                                                                                                                                                                                                                                                                                                                 | 3-15                                         |

|   | GPIB MATLAB Structure Reference                                                                                                                                                                                                                                                                                                                                 | 3-16                                         |

|   | GPIB Initialization and Termination Message Structures                                                                                                                                                                                                                                                                                                          | 3-17                                         |

|   | GPIB Send/Receive Message Structure                                                                                                                                                                                                                                                                                                                             | 3-18                                         |

|   | Shortcuts and Features for Messages                                                                                                                                                                                                                                                                                                                             | 3-21                                         |

|   | Supported Data Types for Message Fields                                                                                                                                                                                                                                                                                                                         | 3-23                                         |

| Λ | l |

|---|---|

|   |   |

| Introduction                                             |

|----------------------------------------------------------|

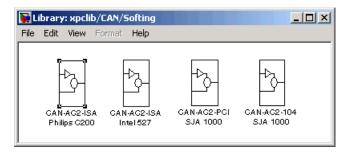

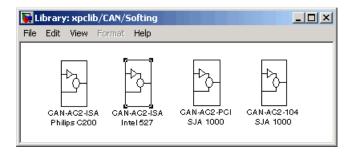

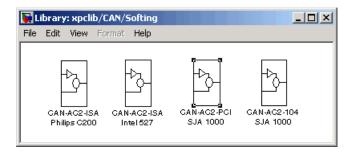

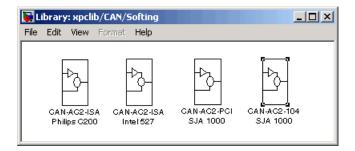

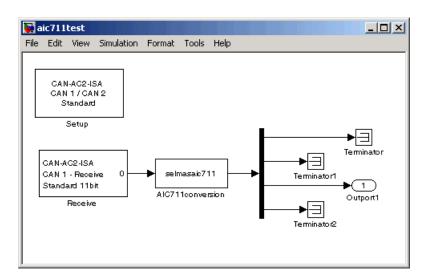

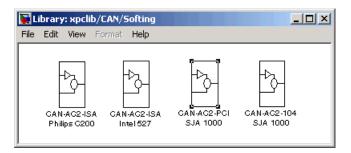

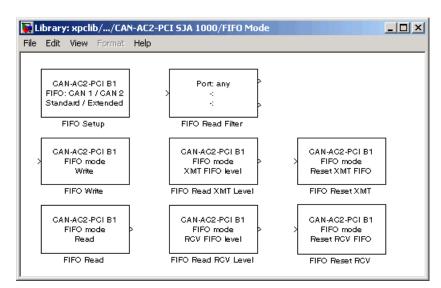

| xPC Target CAN Library                                   |

| CAN-AC2 4-                                               |

| CAN-AC2-PCI 4-                                           |

| CAN-AC2-104                                              |

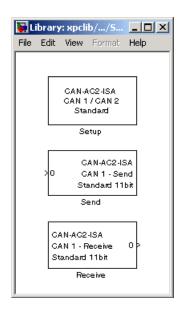

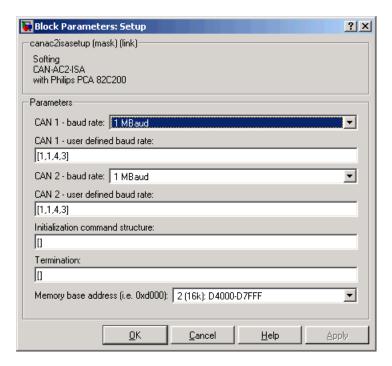

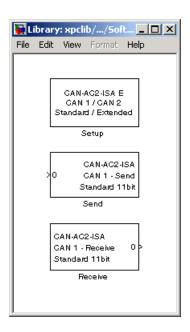

| CAN Driver Blocks for the CAN-AC2 (ISA) with Philips     |

| PCA 82C200 CAN Controller 4-                             |

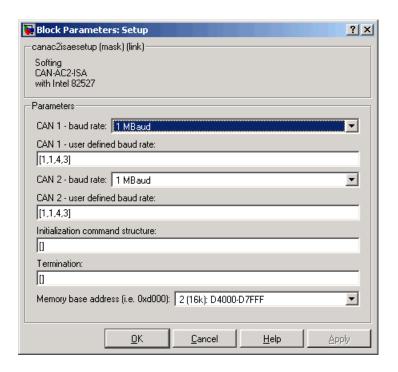

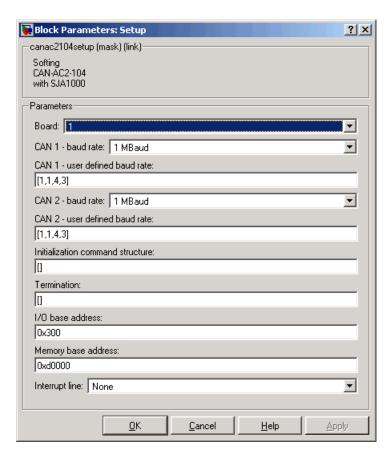

| Setup Driver Block                                       |

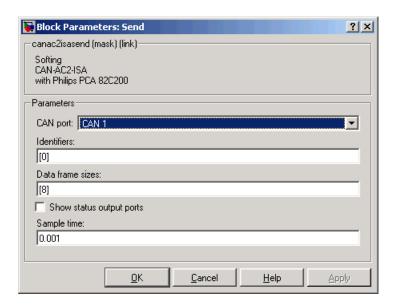

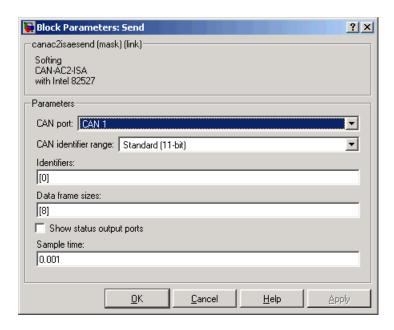

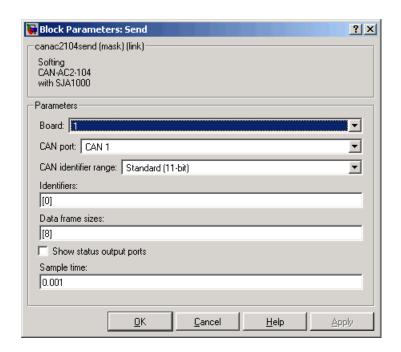

| Send Driver Block 4-1                                    |

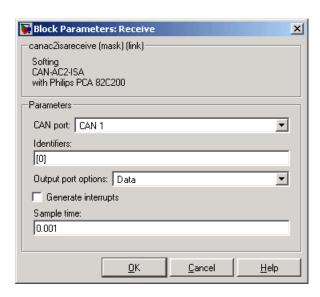

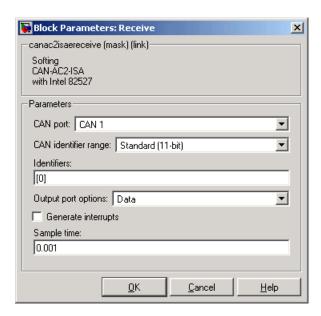

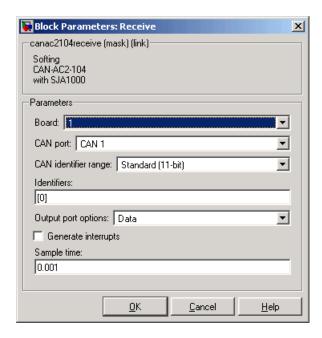

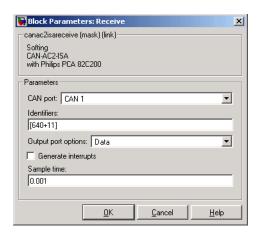

| Receive Driver Block                                     |

| CAN Driver Blocks for the CAN-AC2 (ISA) with Intel 82527 |

| <b>CAN Controller</b>                                    |

| Setup Driver Block                                       |

| Send Driver Block 4-1                                    |

| Receive Driver Block                                     |

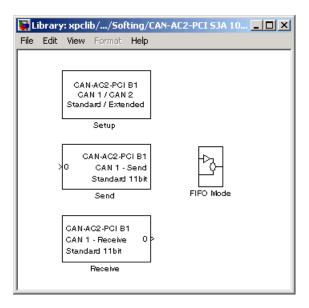

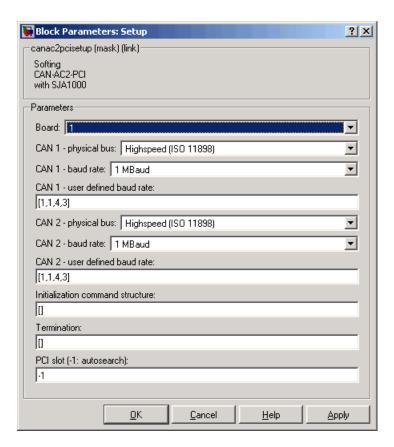

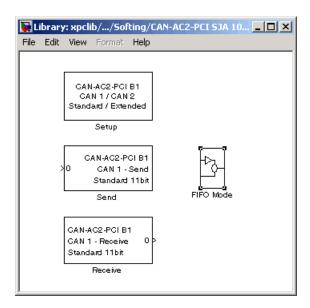

| CAN Driver Blocks for the CAN-AC2-PCI with Philips       |

| SJA1000 CAN Controller                                   |

| Setup Driver Block                                       |

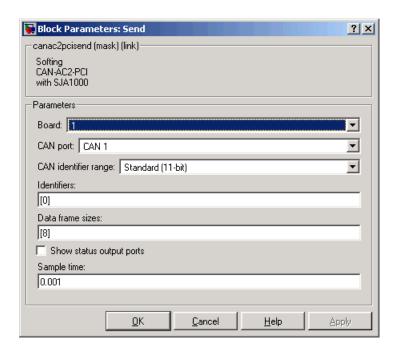

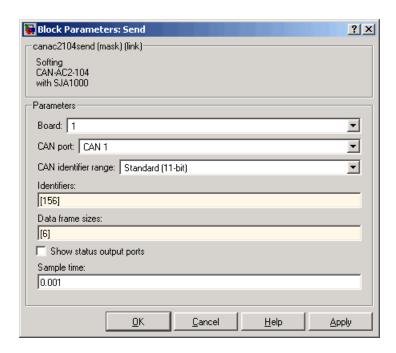

| Send Driver Block 4-2                                    |

| Receive Driver Block                                     |

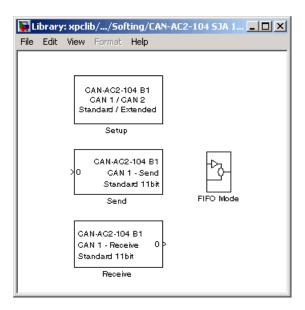

| CAN Driver Blocks for the CAN-AC2-104 (PC/104) with      |

| Philips SJA1000 CAN Controller 4-3                       |

| Setup Driver Block                                       |

| Send Driver Block 4-3                                    |

| Receive Driver Block                                     |

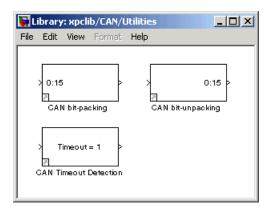

| Constructing and Extracting CAN Data Frames 4-3          |

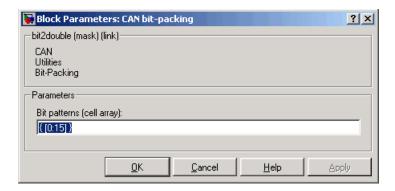

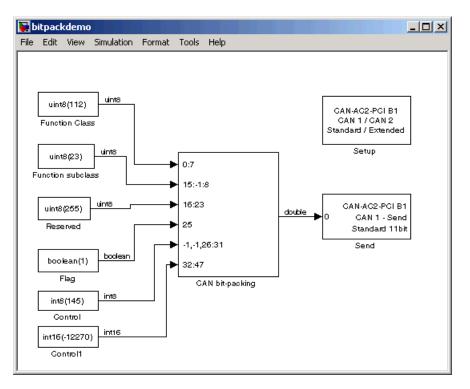

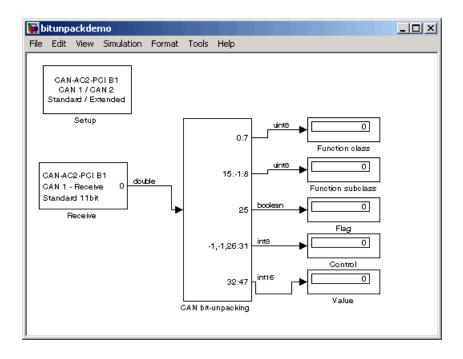

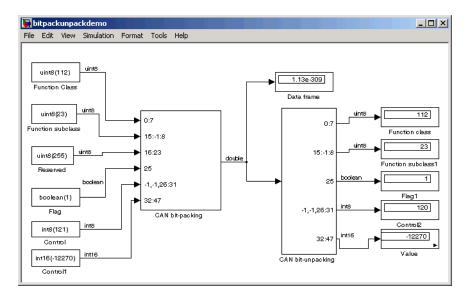

| CAN Bit-Packing Block                                    |

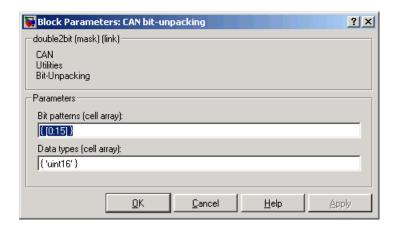

| CAN Bit-Unpacking Block                                  |

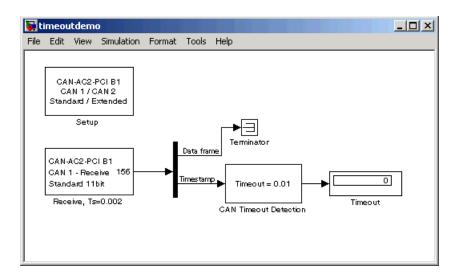

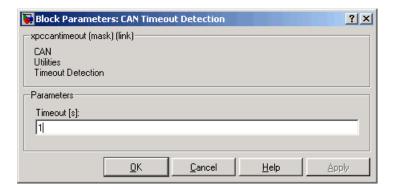

| Detecting Time-Outs When Receiving CAN Messages 4-4      |

| CAN Timeout Detection Block                              |

| <b>Model Execution Driven by CAN Messages</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| (Interrupt Capability of CAN Receive Blocks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-49                 |

| CAN-AC2 (ISA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-49                 |

| CAN-AC2-PCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-50                 |

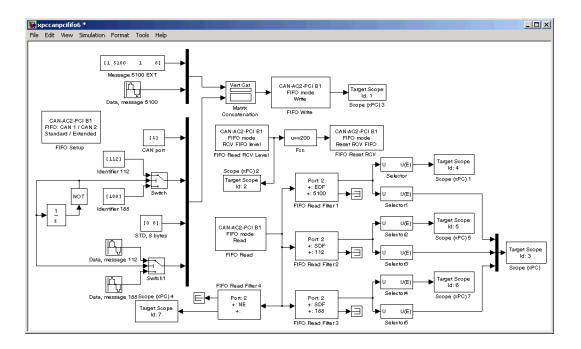

| (Interrupt Capability of CAN Receive Blocks)       4-CAN-AC2 (ISA)         CAN-AC2 (ISA)       4-CAN-AC2-PCI         CAN-AC2-104 (PC/104)       4-CAN-AC2-104 (PC/104)         Defining Initialization and Termination CAN Messages       4-CAN-AC2 and CANopen Devices         CAN-AC2 and CANopen Devices       4-CAN-AC2 and CANopen Devices         Introduction       5         FIFO Mode Drivers for CAN Boards from Softing       5         CAN FIFO Driver Blocks for the CAN-AC2-PCI with       5         FIFO Setup Driver Block       5 | <b>4-5</b> 1         |

| Defining Initialization and Termination CAN Messag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | es . <b>4-5</b> 3    |

| Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-54                 |

| CAN-AC2 and CANopen Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-55                 |

| CAN I/O Support for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r FIFO               |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-2                  |

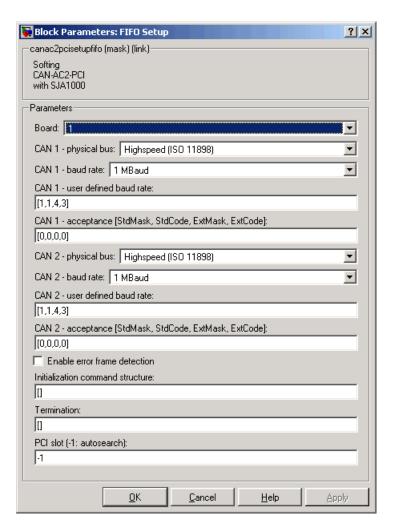

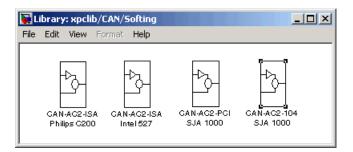

| FIFO Mode Drivers for CAN Boards from Softing $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>5-</b> 3          |

| CAN FIFO Driver Blocks for the CAN-AC2-PCI with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

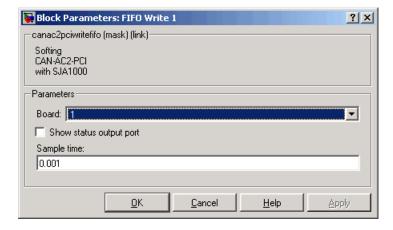

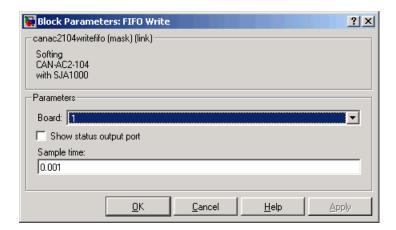

| FIFO Write Driver Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

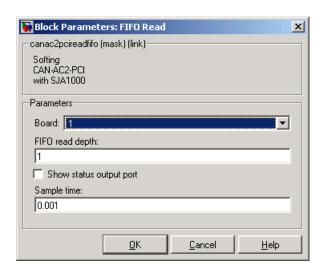

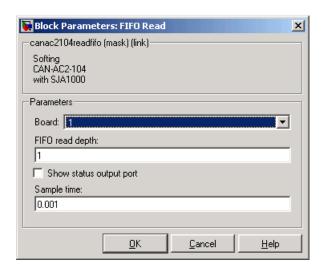

| FIFO Read Driver Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-15                 |

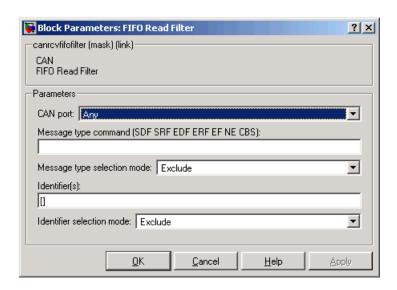

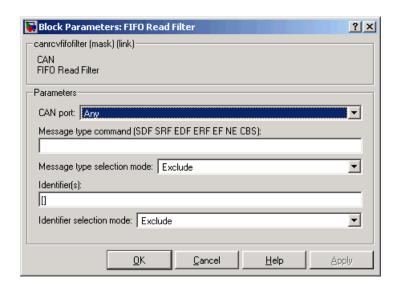

| FIFO Read Filter Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |

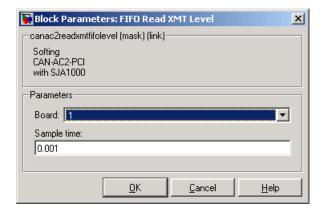

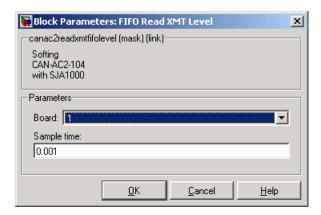

| FIFO Read XMT Level Driver Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-16                 |

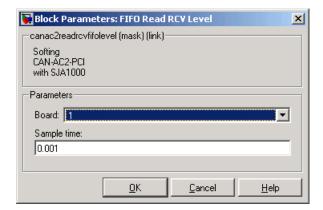

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-16                 |

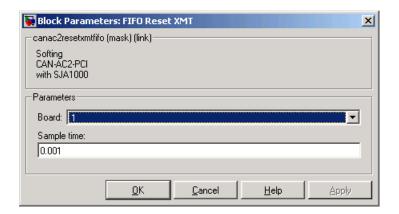

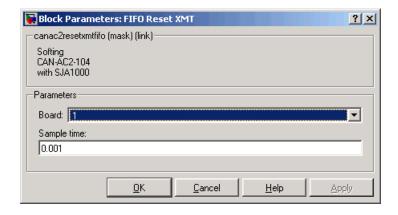

| FIFO Reset XMT Driver Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-16<br>5-18<br>5-19 |

| FIFO Reset XMT Driver Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-16<br>5-18<br>5-19 |

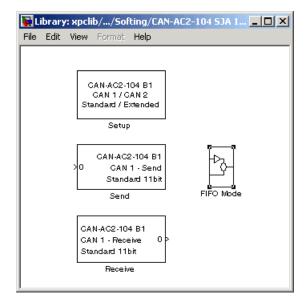

| • | CAN FIFO Driver Blocks for the CAN-AC2-104 with                                                                                                                                  |                                                    |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| ] | Philips SJA1000 CAN Controller                                                                                                                                                   | <b>5-22</b>                                        |

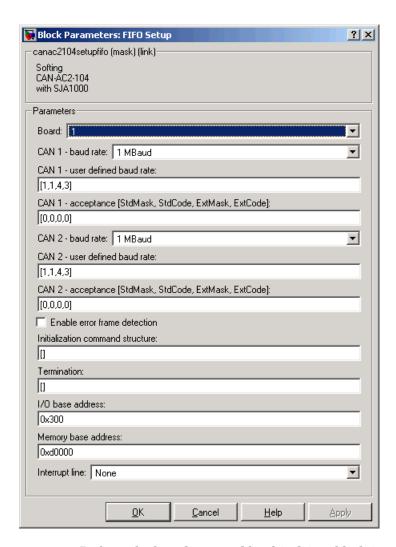

|   | FIFO Setup Driver Block                                                                                                                                                          | <b>5-23</b>                                        |

|   | FIFO Write Driver Block                                                                                                                                                          |                                                    |

|   | FIFO Read Driver Block                                                                                                                                                           | <b>5-29</b>                                        |

|   | FIFO Read Filter Block                                                                                                                                                           |                                                    |

|   | FIFO Read XMT Level Driver Block                                                                                                                                                 |                                                    |

|   | FIFO Reset XMT Driver Block                                                                                                                                                      |                                                    |

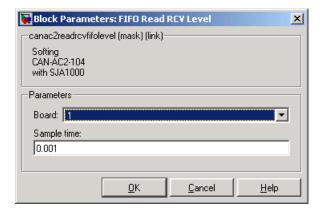

|   | FIFO Read RCV Level Driver Block                                                                                                                                                 | 5-36                                               |

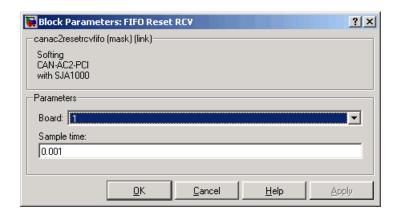

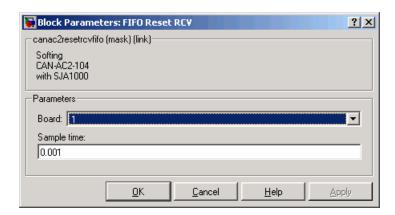

|   | FIFO Reset RCV Driver Block                                                                                                                                                      | 5-36                                               |

| I | Acceptance Filters                                                                                                                                                               | 5-38                                               |

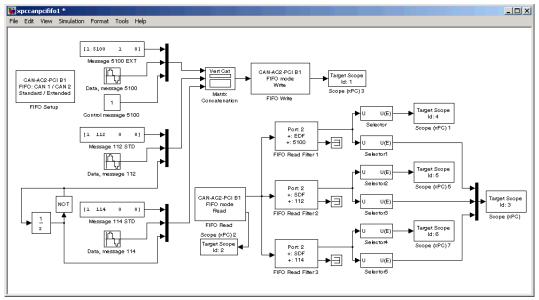

| ] | Examples                                                                                                                                                                         | 5-40                                               |

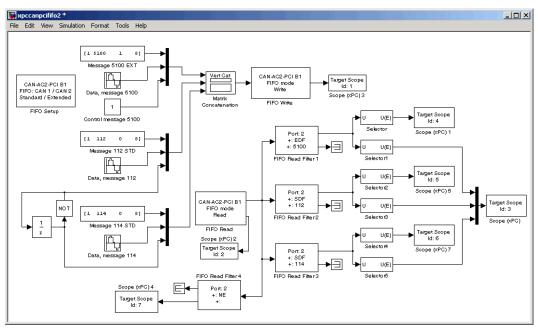

|   | Example 1                                                                                                                                                                        | <b>5-40</b>                                        |

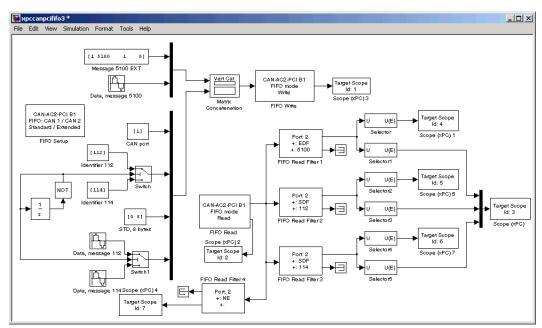

|   | Example 2                                                                                                                                                                        | <b>5-42</b>                                        |

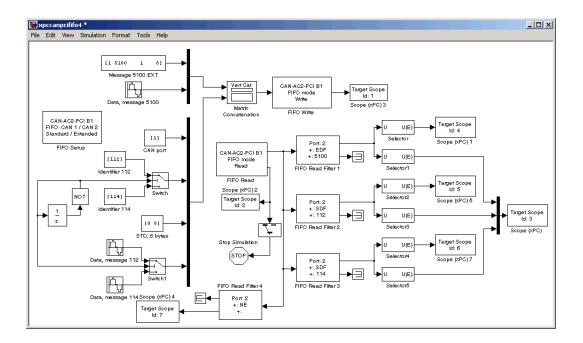

|   | Example 3                                                                                                                                                                        | <b>5-43</b>                                        |

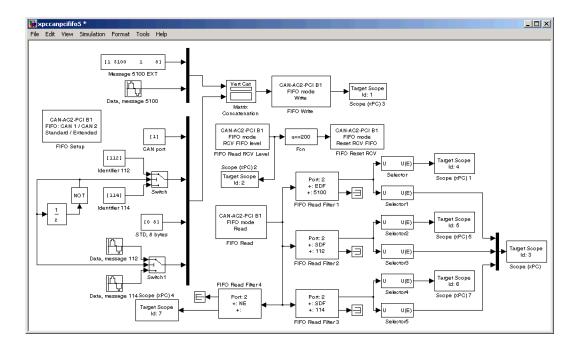

|   | Example 4                                                                                                                                                                        | <b>5-44</b>                                        |

|   | Example 5                                                                                                                                                                        | 5-44                                               |

|   | Ziidiii pie o                                                                                                                                                                    | 0 11                                               |

|   | Example 6                                                                                                                                                                        |                                                    |

| 1 | _                                                                                                                                                                                | 5-45<br>ort<br>. 6-2<br>. 6-4                      |

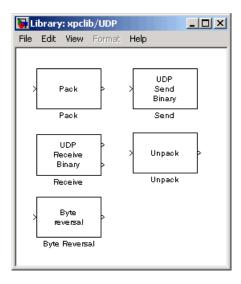

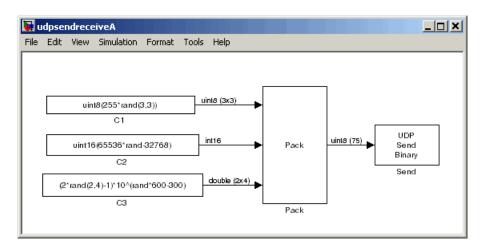

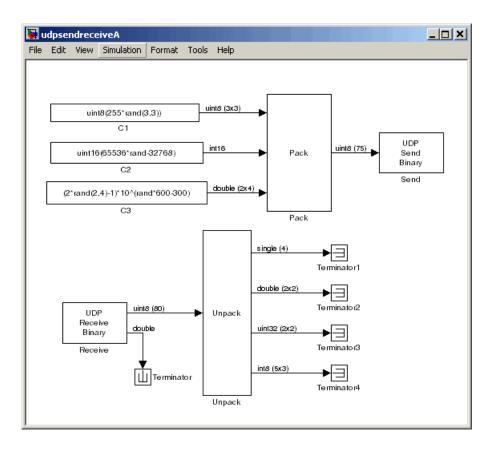

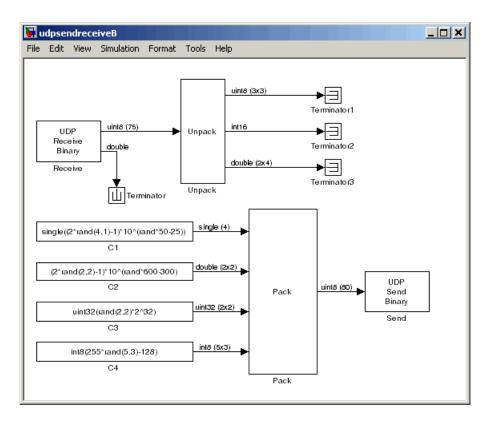

|   | UDP I/O Supp  User Datagram Protocol (UDP)  What Is UDP?  Why UDP?                                                                                                               | 5-45<br>ort<br>. 6-2<br>. 6-2<br>. 6-4             |

|   | UDP I/O Supp  User Datagram Protocol (UDP)  What Is UDP?  Why UDP?  Note on UDP Communication  **PC Target UDP Blocks                                                            | 5-45<br>ort<br>. 6-2<br>. 6-2<br>. 6-4<br>. 6-5    |

|   | UDP I/O Supp  User Datagram Protocol (UDP)  What Is UDP?  Why UDP?  Note on UDP Communication                                                                                    | 5-45  ort  . 6-2 . 6-2 . 6-4 . 6-5                 |

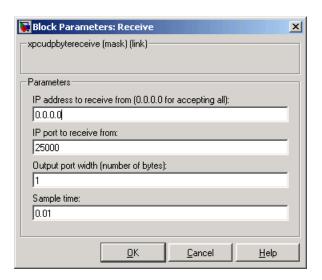

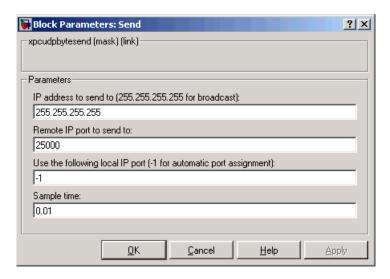

|   | UDP I/O Supp  User Datagram Protocol (UDP)  What Is UDP?  Why UDP?  Note on UDP Communication  **PC Target UDP Blocks  UDP Communication Setup                                   | . 6-2<br>. 6-2<br>. 6-4<br>. 6-4<br>. 6-5<br>. 6-6 |

|   | UDP I/O Supp  User Datagram Protocol (UDP)  What Is UDP?  Why UDP?  Note on UDP Communication  xPC Target UDP Blocks  UDP Communication Setup  UDP Receive Block                 | 5-45  Ort  . 6-2 . 6-2 . 6-4 . 6-5 . 6-5 . 6-6     |

|   | UDP I/O Supp  User Datagram Protocol (UDP)  What Is UDP?  Why UDP?  Note on UDP Communication  xPC Target UDP Blocks  UDP Communication Setup  UDP Receive Block  UDP Send Block | 5-45  ort  . 6-2 . 6-4 . 6-5 . 6-5 . 6-6 . 6-8     |

|               | Aerospace I/O Suppo      |

|---------------|--------------------------|

| Condor        |                          |

|               | eristics                 |

|               | 20 Initialize            |

| Condor CEI-x2 | 20 Send                  |

| Condor CEI-x2 | 20 Receive               |

| Encode ARING  | C 429 Words for Send     |

| Decode ARINO  | C 429 Words from Receive |

|               | Access                   |

|               | atchdog Timer            |

|               | ADDI-DA'                 |

|               |                          |

| 1 | 1 | • |

|---|---|---|

| ı | l | J |

|     | Adlink PCI-8133       10-9         PCI-8133 3-Phase PWM       10-9                                                                                            |          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | Adlink PCI-6208A       10-8         PCI-6208A Analog Output       10-8         PCI-6208A Digital Input       10-8         PCI-6208A Digital Output       10-8 | 5<br>7   |

| 1 [ | Advantech                                                                                                                                                     | <u>l</u> |

|     | PCL-1800                                                                                                                                                      | 3        |

|     | PCL-1800 Analog Input (A/D)                                                                                                                                   |          |

|     | PCL-1800 Analog Output (D/A)                                                                                                                                  |          |

|     | PCL-1800 Digital Input                                                                                                                                        |          |

|     | PCL-1800 Digital Output                                                                                                                                       |          |

|     | PCL-711B                                                                                                                                                      | 8        |

|     | PCL-711B Analog Input (A/D)                                                                                                                                   | 8        |

|     | PCL-711B Analog Output (D/A) 11-10                                                                                                                            | 0        |

|     | PCL-711B Digital Input                                                                                                                                        | 0        |

|     | PCL-711B Digital Output 11-1                                                                                                                                  | 1        |

|     | PCL-726 11-12                                                                                                                                                 | 2        |

|     | PCL-726 Analog Output (D/A)                                                                                                                                   | 2        |

|     | PCL-726 Digital Input                                                                                                                                         | 4        |

|     | PCL-726 Digital Output 11-16                                                                                                                                  | 5        |

|     | PCL-727 11-10                                                                                                                                                 | 6        |

|     | PCL-727 Analog Output (D/A)                                                                                                                                   | 6        |

|     | PCL-727 Digital Input                                                                                                                                         |          |

|     | PCL-727 Digital Output                                                                                                                                        | 9        |

| PCL-728                         | 0        |

|---------------------------------|----------|

| PCL-728 Analog Output (D/A)     | 0        |

|                                 |          |

| PCL-812 11-2                    | 2        |

| PCL-812 Analog Input (A/D)      | 2        |

| PCL-812 Analog Output (D/A)     | 4        |

| PCL-812 Digital Input           |          |

| PCL-812 Digital Output 11-2     | 6        |

| 8                               |          |

| PCL-812PG                       | 7        |

| PCL-812PG Analog Input (A/D)    | -        |

| PCL-812PG Analog Output (D/A)   |          |

| PCL-812PG Digital Input         | -        |

| PCL-812PG Digital Output        |          |

| 1 CD 0121 G Digital Output 11-0 | _        |

| PCL-818                         | 9        |

| PCL-818 Analog Input (A/D)      |          |

| PCL-818 Analog Output (D/A)     |          |

| PCL-818 Digital Input           | _        |

| PCL-818 Digital Output          |          |

| FOL-010 Digital Output 11-3     | O        |

| PCL-818H                        | 0        |

|                                 | _        |

| PCL-818H Analog Input (A/D)     |          |

| PCL-818H Analog Output (D/A)    |          |

| PCL-818H Digital Input          | _        |

| PCL-818H Digital Output 11-4    | 2        |

|                                 |          |

| PCL-818HD                       | _        |

| PCL-818HD Analog Input (A/D)    | _        |

| PCL-818HD Analog Output (D/A)   |          |

| PCL-818HD Digital Input         |          |

| PCL-818HD Digital Output        | 7        |

|                                 |          |

| PCL-818HG 11-4                  | 8        |

| PCL-818HG Analog Input (A/D)    | 8        |

| PCL-818HG Analog Output (D/A)   | 0        |

| PCL-818HG Digital Input 11-5    | 1        |

| PCL-818HG Digital Output 11-5   | <b>2</b> |

| Analo                    |

|--------------------------|

| THILL                    |

| AIM12                    |

| AIM12 Analog Input (A/D) |

| AIM12 Digital Input      |

| AIM12 Digital Output     |

| AIM16                    |

| AIM16 Analog Input (A/D) |

| AIM16 Digital Input      |

| BittWa                   |

|                          |

| Audio-PMC+               |

| Audio-PMC+ Analog Input  |

| Audio-PMC+ Analog Output |

| В                        |

### 15

| Contec AD12-16(PCI)                | . 15-3       |

|------------------------------------|--------------|

| AD12-16(PCI) Analog Input (A/D)    |              |

| AD12-16(PCI) Digital Input         |              |

| AD12-16(PCI) Digital Output        |              |

| Contec AD12-16(PCI)E               | . 15-8       |

| AD12-16(PCI)E Analog Input (A/D)   | . 15-8       |

| AD12-16(PCI)E Analog Output (D/A)  | 15-10        |

| Contec AD12-16U(PCI)E              | 15-11        |

| AD12-16U(PCI)E Analog Input (A/D)  | 15-11        |

| AD12-16U(PCI)E Analog Output (D/A) | 15-12        |

| Contec ADI12-16(PCI)               | 15-14        |

| ADI12-16(PCI) Analog Input (A/D)   | 15-14        |

| Contec AD12-64(PCI)                | 15-16        |

| AD12-64(PCI) Analog Input (A/D)    | 15-16        |

| AD12-64(PCI) Digital Input         | <b>15-18</b> |

| AD12-64(PCI) Digital Output        | 15-19        |

| Contec AD16-16(PCI)E               | 15-21        |

| AD16-16(PCI)E Analog Input (A/D)   | <b>15-21</b> |

| AD16-16(PCI)E Analog Output (D/A)  | 15-22        |

| Contec DA12-4(PCI)                 | 15-24        |

| DA12-4(PCI) Analog Output (D/A)    | 15-24        |

| Contec DA12-16(PCI)                | 15-26        |

| DA12-16(PCI) Analog Output (D/A)   | 15-26        |

| Contec PIO-32/32T(PCI)             | 15-28        |

| PIO-32/32T(PCI) Digital Input      | <b>15-28</b> |

| PIO-32/32T(PCI) Digital Output     |              |

| Contec CNT24-4D(PCI)               | 15-31        |

| CNT24-4D(PCI) Incremental Encoder  |              |

# 16 🗆

| DT2821                           | 16-3          |

|----------------------------------|---------------|

| DT2821 Analog Input (A/D)        | 16-3          |

| DT2821 Analog Output (D/A)       |               |

| DT2821 Digital Input             |               |

| DT2821 Digital Output            |               |

| DT2821-F-8DI                     | 16-8          |

| DT2821-F-8DI Analog Input (A/D)  | <b>16-8</b>   |

| DT2821-F-8DI Analog Output (D/A) | 16-10         |

| DT2821-F-8DI Digital Input       | 16-11         |

| DT2821-F-8DI Digital Output      |               |

| DT2821-G-8DI                     | 16-13         |

|                                  | 16-13         |

|                                  | 16-15         |

|                                  | 16-16         |

|                                  | 16-17         |

| DT2821-F-16SE                    | 16-18         |

|                                  | 16-18         |

|                                  | 16-20         |

|                                  | 16-21         |

|                                  | 16-22         |

| DT2821-G-16SE                    | 16-23         |

|                                  | 16-23         |

|                                  | 16-25         |

|                                  | 16-26         |

|                                  | 16-27         |

| DT2823                           | 16-28         |

| DT2823 Analog Input (A/D)        | <b>16-2</b> 8 |

|                                  | 16-29         |

|                                  | <b>16-3</b> 0 |

|                                  | 16-31         |

| Diamond-MM-16-AT                  | . 17-9 |

|-----------------------------------|--------|

| MM-16-AT Analog Input (A/D)       | 17-10  |

| MM-16-AT Analog Output (D/A)      | 17-11  |

| MM-16-AT Digital Input            | 17-12  |

| MM-16-AT Digital Output           |        |

| Diamond-MM-32-AT                  | 17-15  |

| MM-32-AT Analog Input (A/D)       | 17-16  |

| MM-32-AT Frame Analog Input (A/D) | 17-17  |

| MM-32-AT Analog Output (D/A)      | 17-20  |

| MM-32-AT Digital Input            | 17-21  |

| MM-32-AT Digital Output           | 17-22  |

| Garnet-MM                         | 17-25  |

| Garnet-MM Digital Input           | 17-25  |

| Garnet-MM Digital Output          | 17-26  |

| Onyx-MM                           | 17-28  |

| Onyx-MM Digital Input             | 17-28  |

| Onyx-MM Digital Output            |        |

| Onyx-MM-DIO                       | 17-31  |

| Onyx-MM-DIO Digital Input         | 17-31  |

| Onyx-MM-DIO Digital Output        |        |

| Prometheus                        | 17-34  |

| Prometheus Analog Input (A/D)     |        |

| Prometheus Analog Output (D/A)    |        |

| Prometheus Digital Input          |        |

| Promothous Digital Output         |        |

| Quartz-MM 5                         | 17-40        |

|-------------------------------------|--------------|

| Quartz-MM 5 Digital Input           | 17-41        |

| Quartz-MM 5 Digital Output          | 17-42        |

| Quartz-MM5 Counter PWM              | 17-43        |

| Quartz-MM5 Counter PWM & ARM        | 17-44        |

| Quartz-MM5 Counter FM               | 17-46        |

| Quartz-MM5 Counter FM & ARM         | 17-47        |

| Quartz-MM5 PWM Capture              | 17-49        |

| Quartz-MM5 FM Capture               | 17-50        |

| Quartz-MMxx                         | 17-51        |

| Quartz-MM 10                        | 17-52        |

| Quartz-MM 10 Digital Input          | <b>17-53</b> |

| Quartz-MM 10 Digital Output         | 17-54        |

| Quartz-MM 10 Counter PWM            | 17-54        |

| Quartz-MM 10 Counter PWM & ARM      | 17-56        |

| Quartz-MM 10 Counter FM             | 17-57        |

| Quartz-MM 10 Counter FM & ARM       | 17-59        |

| Quartz-MM 10 PWM Capture            | <b>17-60</b> |

| Quartz-MM 10 FM Capture             | 17-61        |

| Quartz-MMxx                         | 17-62        |

| Ruby-MM                             | 17-63        |

| Diamond Ruby-MM Analog Output (D/A) | <b>17-63</b> |

| Diamond Ruby-MM Digital Input       | 17-65        |

| Diamond Ruby-MM Digital Output      | 17-66        |

| Ruby-MM-416                         | 17-68        |

| Ruby-MM-416 Analog Output (D/A)     | <b>17-68</b> |

| Ruby-MM-416 Digital Input           | <b>17-70</b> |

| Ruby-MM-416 Digital Output          | 17-71        |

| Ruby-MM-1612                        | 17-73        |

| Ruby-MM-1612 Analog Output (D/A)    | <b>17-73</b> |

| Ruby-MM-1612 Digital Input          | 17-76        |

| Ruby-MM-1612 Digital Output         | 17-77        |

| 1 | 0 |

|---|---|

| ı | Ō |

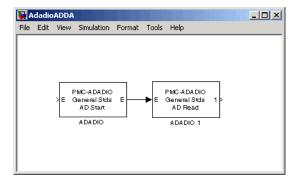

| ( | Overview of PMC-ADADIO Functionality 18                  | -2 |

|---|----------------------------------------------------------|----|

|   | A/D Blocks                                               |    |

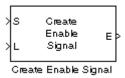

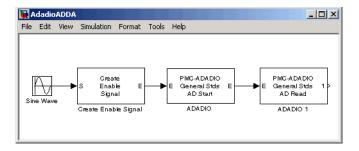

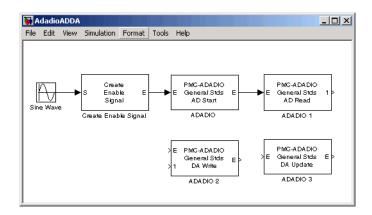

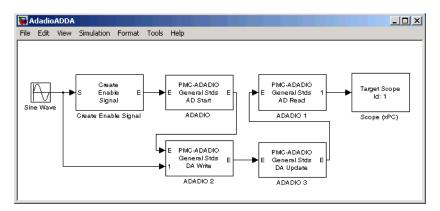

|   | Create Enable Signal Blocks                              | -5 |

|   | D/A Blocks                                               | -8 |

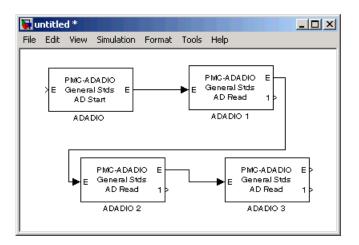

|   | Interleaving Analog Input and Analog Output Blocks 18-1  | 10 |

|   | Using Multiple Boards for Simultaneous Analog to Digital |    |

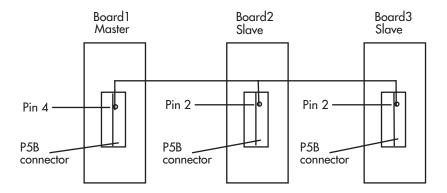

|   | Conversion                                               | 12 |

| I | PMC-ADADIO                                               | 14 |

|   | PMC-ADADIO Analog Input (A/D) Start 18-1                 | 15 |

|   | PMC-ADADIO Analog Input (A/D) Read 18-1                  | 16 |

|   | PMC-ADADIO Analog Output (D/A) Write 18-1                | 17 |

|   | PMC-ADADIO Analog Output (D/A) Update 18-2               |    |

|   | PMC-ADADIO Digital Input 18-2                            |    |

|   | PMC-ADADIO Digital Output 18-2                           | 22 |

|   | Create Enable Signal                                     | 24 |

| ŀ | PMC-16AO-12 18-2                                         | 25 |

|   | PMC-16AO-12 Analog Output                                |    |

|   |                                                          |    |

|   | Humusof                                                  | t  |

|   |                                                          |    |

| 1 | AD 512 19                                                | -2 |

| - | AD 512 Analog Input (A/D)                                |    |

|   | AD 512 Analog Output (D/A)                               |    |

|   | AD 512 Digital Input                                     |    |

|   |                                                          |    |

|      | $\sim$ |

|------|--------|

| - 44 |        |

|      |        |

|      | ~      |

**21**

| DAS-1800HR                                             |

|--------------------------------------------------------|

| DAS-1800HR Analog Input (A/D)                          |

| DAS-1800HR Digital Input                               |

| DAS-1800HR Digital Output                              |

| 2130 2000121 2381001 0 000 000 1000 1000 1000 1000 100 |

| KCPI-1801HC 20-7                                       |

| KPCI-1801HC Analog Input (A/D)                         |

| KPCI-1801HC Analog Output (D/A) 20-10                  |

| KPCI-1801HC Digital Input 20-11                        |

| KPCI-1801HC Digital Output                             |

|                                                        |

| KPCI-1802HC                                            |

| KPCI-1802HC Analog Input (A/D) 20-15                   |

| KPCI-1802HC Analog Output (D/A) 20-17                  |

| KPCI-1802HC Digital Input                              |

| KPCI-1802HC Digital Output 20-19                       |

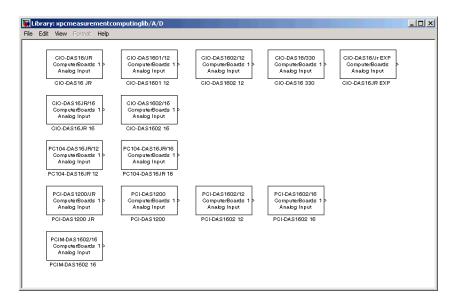

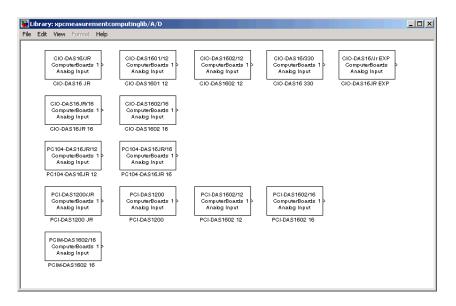

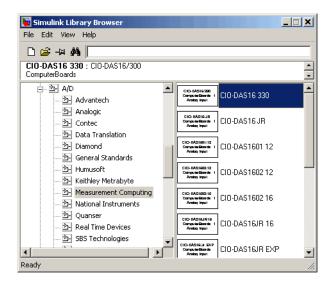

| Measurement Computing (Formerly<br>ComputerBoards)     |

|                                                        |

| GLO CIMPOT                                             |

| CIO-CTR05                                              |

| CIO-CTR05 Counter PWM                                  |

| CIO-CTR05 Counter PWM & ARM                            |

| CIO-CTR05 Counter FM                                   |

| CIO-CTR05 Counter FM & ARM                             |

| CIO-CTR05 PWM Capture                                  |

| CIO-CTR05 Frequency Capture                            |

| CIO-CTRxx                                              |

| CIO-CTR10                                             | 21-14         |

|-------------------------------------------------------|---------------|

| CIO-CTR10 Counter PWM                                 | 21-15         |

| CIO-CTR10 Counter PWM & ARM                           | 21-16         |

| CIO-CTR10 Counter FM                                  | 21-18         |

| CIO-CTR10 Counter FM & ARM                            | 21-19         |

| CIO-CTR10 PWM Capture                                 | 21-21         |

| CIO-CTR10 Frequency Capture                           | 21-22         |

| CIO-CTRxx                                             | 21-22         |

| CIO-DAC08 (/12)                                       | 21-23         |

| CIO-DAC08 Analog Output (D/A)                         | 21-23         |

| CIO-DAC08/16                                          | 21-25         |

| CIO-DAC08/16 Analog Output (D/A)                      | 21-25         |

| CIO-DAC16 (/12)                                       | 21-27         |

| CIO-DAC16 Analog Output (D/A)                         | 21-27         |

| CIO-DAC16/16                                          | 21-30         |

| CIO-DAC16/16 Analog Output (D/A)                      |               |

| CIO-DAS16/330                                         | 21-33         |

| CIO-DAS16/330 Analog Input (A/D)                      |               |

| CIO-DAS16/JR (/12)                                    | 21-35         |

| CIO-DAS16/JR Analog Input (A/D)                       | 21-36         |

| CIO-DAS16/JR (/12) Analog Input (A/D) with EXP Signal |               |

| Conditioning Board                                    | 21-37         |

| CIO-DAS16JR/16                                        | 21-40         |

| CIO-DAS16JR/16 Analog Input (A/D)                     | 21-41         |

| CIO-DAS1601/12                                        | 21-42         |

| CIO-DAS1601/12 Analog Input (A/D)                     | <b>21-4</b> 3 |

| CIO-DAS1601/12 Analog Output (D/A)                    | 21-44         |

| CIO-DAS1601/12 Digital Input                          | 21-45         |

| CIO-DAS1601/12 Digital Output                         | 21-46         |

| CIO-DAS1602/12                      | 21-49 |

|-------------------------------------|-------|

| CIO-DAS1602/12 Analog Input (A/D)   | 21-50 |

| CIO-DAS1602/12 Analog Output (D/A)  | 21-51 |

| CIO-DAS1602/12 Digital Input        | 21-52 |

| CIO-DAS1602/12 Digital Output       |       |

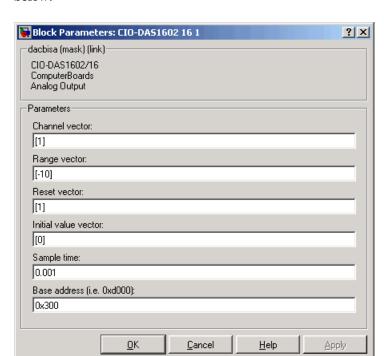

| CIO-DAS1602/16                      | 21-55 |

| CIO-DAS1602/16 Analog Input (A/D)   |       |

| CIO-DAS1602/16 Analog Output (D/A)  | 21-57 |

| CIO-DAS 1602/16 Digital Input       |       |

| CIO DAS1602/16 Digital Output       |       |

| CIO-DDA06 (/12)                     | 21-61 |

| CIO-DDA06 (/12) Analog Output (D/A) | 21-62 |

| CIO-DDA06 (/12) Digital Input       |       |

| CIO-DDA06 (/12) Digital Output      |       |

| CIO-DDA06/16                        | 21-67 |

| CIO-DDA06/16 Analog Output (D/A)    | 21-68 |

| CIO-DDA06/16 Digital Input          |       |

| CIO-DDA06/16 Digital Output         |       |

| CIO-DIO24                           | 21-73 |

| CIO-DIO24 Digital Input             | 21-73 |

| CIO-DIO24 Digital Output            | 21-74 |

| CIO-DIO24 Signal Conditioning       | 21-76 |

| CIO-DIO24H                          | 21-77 |

| CIO-DIO24H Digital Input            | 21-77 |

| CIO-DIO24H Digital Output           | 21-78 |

| CIO-DIO48                           | 21-80 |

| CIO-DIO48 Digital Input             | 21-80 |

| CIO-DIO48 Digital Output            | 21-81 |

| CIO-DIO48H                          |       |

| CIO-DIO48H Digital Input            | 21-84 |

| CIO-DIO48H Digital Output           | 21-86 |

| CIO-DIO96                                 | 21-88         |

|-------------------------------------------|---------------|

| CIO-DIO96 Digital Input                   | 21-88         |

| CIO-DIO96 Digital Output                  |               |

| CIO-DIO192                                | 21-92         |

| CIO-DIO192 Digital Input                  | 21-92         |

| CIO-DIO192 Digital Output                 | <b>21-9</b> 3 |

| CIO-DO24DD                                |               |

| CIO-DO24DD Digital Output                 | 21-96         |

| CIO-PDISO16                               |               |

| CIO-PDISO16 Digital Input                 |               |

| CIO-PDISO16 Digital Output                | 21-99         |

| CIO-QUAD02                                |               |

| CIO-QUAD02 Incremental Encoder            |               |

| CIO-QUAD02 Incremental Encoder (Obsolete) | 21-106        |

| CIO-QUAD04                                |               |

| CIO-QUAD04 Incremental Encoder            |               |

| CIO-QUAD04 Incremental Encoder (Obsolete) | 21-114        |

| PC104-DAC06 (/12)                         |               |

| PC104-DAC06 (/12) Analog Output (D/A)     | 21-117        |

| PC104-DAS16JR/12                          |               |

| PC104-DAS16JR/12 Analog Input (A/D)       |               |

| PC104-DAS16JR/12 Digital Input            |               |

| PC104-DAS16JR/12 Digital Output           | 21-122        |

| PC104-DAS16JR/16                          |               |

| PC104-DAS16JR/16 Analog Input (A/D)       |               |

| PC104-DAS16JR/16 Digital Input            |               |

| PC104-DAS16JR/16 Digital Output           | 21-126        |

| PC104-DIO48                               |               |

| PC104-DIO48 Digital Input                 |               |

| PC104-DIO48 Digital Output                | 21-129        |

| PCI-CTR05                            | 21-131 |

|--------------------------------------|--------|

| PCI-CTR05 Counter PWM                | 21-132 |

| PCI-CTR05 Counter PWM & ARM          | 21-133 |

| PCI-CTR05 Counter FM                 | 21-135 |

| PCI-CTR05 Counter FM & ARM           | 21-137 |

| PCI-CTR05 PWM Capture                | 21-138 |

| PCI-CTR05 Frequency Capture          | 21-139 |

| PCI-CTRxx                            |        |

|                                      |        |

| PCI-DAS1200                          | 21-141 |

| PCI-DAS1200 Analog Input (A/D)       | 21-141 |

| PCI-DAS1200 Analog Output (D/A)      | 21-143 |

| PCI-DAS1200 Digital Input            | 21-144 |

| PCI-DAS1200 Digital Output           | 21-146 |

|                                      |        |

| PCI-DAS1200/JR                       | 21-148 |

| PCI-DAS1200/JR Analog Input (A/D)    | 21-148 |

| PCI-DAS1200/JR Digital Input         | 21-149 |

| PCI-DAS1200/JR Digital Output        | 21-151 |

| PCI-DAS1602/12                       | 91 159 |

| PCI-DAS1602/12 Analog Input (A/D)    |        |

| PCI-DAS1602/12 Analog Dutput (A/D)   |        |

| PCI-DAS 1602/12 Alialog Output (D/A) |        |

|                                      |        |

| PCI-DAS1602/12 Digital Output        | 21-198 |

| PCI-DAS1602/16                       | 21-160 |

| PCI-DAS1602/16 Analog Input (A/D)    |        |

| PCI-DAS1602/16 Analog Output (D/A)   |        |

| PCI-DAS 1602/16 Digital Input        |        |

| PCI-DAS1602/16 Digital Output        |        |

| <del>-</del>                         |        |

| PCI-DDA02/12                         | 21-167 |

| PCI-DDA02/12 Analog Output (D/A)     |        |

| PCI-DDA02/12 Digital Input           |        |

| PCI-DDA02/12 Digital Output          |        |

| PCI-DDA02/16                     | 21-173 |

|----------------------------------|--------|

| PCI-DDA02/16 Analog Output (D/A) | 21-173 |

| PCI-DDA02/16 Digital Input       |        |

| PCI-DDA02/16 Digital Output      | 21-176 |

| PCI-DDA04/12                     | 21-179 |

| PCI-DDA04/12 Analog Output (D/A) | 21-179 |

| PCI-DDA04/12 Digital Input       | 21-181 |

| PCI-DDA04/12 Digital Output      | 21-182 |

| PCI-DDA04/16                     | 21-185 |

| PCI-DDA04/16 Analog Output (D/A) | 21-185 |

| PCI-DDA04/16 Digital Input       | 21-187 |

| PCI-DDA04/16 Digital Output      | 21-188 |

| PCI-DDA08/12                     | 21-191 |

| PCI-DDA08/12 Analog Output (D/A) |        |

| PCI-DDA08/12 Digital Input       |        |

| PCI-DDA08/12 Digital Output      |        |

| PCI-DDA08/16                     | 21-197 |

| PCI-DDA08/16 Analog Output (D/A) |        |

| PCI-DDA08/16 Digital Input       |        |

| PCI-DDA08/16 Digital Output      |        |

| PCI-DIO24                        | 21-203 |

| PCI-DIO24 Digital Input          |        |

| PCI-DIO24 Digital Output         |        |

| PCI-DIO24 Signal Conditioning    |        |

| PCI-DIO24H                       | 21-207 |

| PCI-DIO24H Digital Input         |        |

| PCI-DIO24H Digital Output        |        |

| PCI-DIO48H                       | 21-211 |

| PCI-DIO48H Digital Input         |        |

| PCI-DIO48H Digital Output        |        |

| PCI-DIO96H                                | 21-215 |

|-------------------------------------------|--------|

| PCI-DIO96H Digital Input                  | 21-215 |

| PCI-DIO96H Digital Output                 |        |

|                                           |        |

| PCI-DIO96                                 | 21-219 |

| PCI-DIO96 Digital Input                   | 21-219 |

| PCI-DIO96 Digital Output                  |        |

|                                           |        |

| PCI-PDIS08                                | 21-223 |

| PCI-PDISO8 Digital Input                  | 21-223 |

| PCI-PDISO8 Digital Output                 | 21-225 |

|                                           |        |

| PCI-PDISO16                               | 21-226 |

| PCI-PDISO16 Digital Input                 |        |

| PCI-PDISO16 Digital Output                |        |

| 8                                         |        |

| PCIM-DAS1602/16                           | 21-229 |

| PCIM-DAS1602/16 Analog Input (A/D)        |        |

| PCIM-DAS1602/16 Analog Output (D/A)       |        |

| PCIM-DAS 1602/16 Digital Input            |        |

| PCIM-DAS1602/16 Digital Output            |        |

|                                           |        |

| PCIM-DDA06/16                             | 21-236 |

| PCIM-DDA06/16 Analog Output (D/A)         |        |

| PCIM-DDA06/16 Digital Input               |        |

| PCIM-DDA06/16 Digital Output              |        |

| Total BB100/10 Bigital output             | 21 200 |

| PCI-DUAL-AC5                              | 21-242 |

| PCI-DUAL-AC5 Digital Input                |        |

| PCI-DUAL-AC5 Digital Output               |        |

| Tot Both Hoo Bigital output               | 21 210 |

| PCI-QUAD04                                | 21-246 |

| PCI-QUAD04 Incremental Encoder            |        |

| PCI-QUAD04 Incremental Encoder (Obsolete) |        |

|                                           |        |

| PCI-DAS-TC                                | 21-254 |

| PCI DAS TC Thermosouple                   |        |

| AT-AO-6                                  | . 22-4        |

|------------------------------------------|---------------|

| AT-AO-6 Analog Output (D/A)              | . 22-4        |

| AT-AO-10                                 | . 22-6        |

| AT-AO-10 Analog Output (D/A)             | . 22-6        |

| PC-DIO-24                                | . 22-8        |

| PC-DIO-24 Digital Input                  | . 22-8        |

| PC-DIO-24 Digital Output                 | . 22-9        |

| PC-TIO-10                                | 22-12         |

| PC-TIO-10 Digital Input                  | 22-12         |

| PC-TIO-10 Digital Output                 | 22-13         |

| PC-TIO-10 Counter PWM                    | 22-15         |

| PC-TIO-10 Counter PWM & ARM              | 22-16         |

| PC-TIO-10 Counter FM                     |               |

| PC-TIO10 Counter FM & ARM                |               |

| PC-TIO10 PWM Capture                     | 22-21         |

| PC-TIO10 FM Capture                      |               |

| PC-TIO-10xx                              |               |

| PCI-6023E                                | 22-23         |

| PCI-6023E Analog Input (A/D)             | <b>22-2</b> 4 |

| PCI-6023E Digital Input                  |               |

| PCI-6023E Digital Output                 |               |

| PCI-6023E Pulse Generation               | 22-28         |

| PCI-6023E Pulse Width/Period Measurement | 22-29         |

| PCI-6024E                                | 22-3          |

| PCI-6024E Analog Input (A/D)             |               |

| PCI-6024E Analog Output (D/A)            |               |

| PCI-6024E Digital Input                  |               |

| PCI-6024E Digital Output                 |               |

| PCI-6024E Pulse Generation               |               |

| PCI-6024E Pulse Width/Period Measurement |               |

| PCI-6025E                                    | 22-40 |

|----------------------------------------------|-------|

| PCI-6025E Analog Input (A/D)                 | 22-41 |

| PCI-6025E Analog Output (D/A)                | 22-43 |

| PCI-6025E and PCI-6025E 8255 Digital Input   | 22-44 |

| PCI-6025E Digital Output                     | 22-45 |

| PCI-6025E Pulse Generation                   | 22-46 |

| PCI-6025E Pulse Width/Period Measurement     | 22-47 |

| PCI-6030E (Formerly PCI-MIO-16XE-10)         | 22-49 |

| PCI-6030E Analog Input (A/D)                 |       |

| PCI-6030E Analog Output (D/A)                |       |

| PCI-6030E Digital Input                      |       |

| PCI-6030E Digital Output                     |       |

| PCI-6030E Pulse Generation                   |       |

| PCI-6030E Pulse Width/Period Measurement     |       |

| PCI-6031E                                    | 22-59 |

| PCI-6031E Analog Input (A/D)                 |       |

| PCI-6031E Analog Output (D/A)                |       |

| PCI-6031E Digital Input                      |       |

| PCI-6031E Digital Output                     |       |

| PCI-6031E Pulse Generation                   |       |

| PCI-6031E Pulse Width/Period Measurement     |       |

| PCI-6040E (Formerly PCI-MIO-16E-4)           | 22-69 |

| PCI-6040E Analog Input (A/D)                 |       |

| PCI-6040E Analog Output (D/A)                |       |

| PCI-6040E Digital Input                      |       |

| PCI-6040E Digital Output                     |       |

| PCI-6040E Pulse Generation                   |       |

| PCI-6040E Pulse Width/Period Measurement     |       |

| PCI/PXI-6052E                                | 22-79 |

| PXI/PCI-6052E Analog Input (A/D)             |       |

| PXI/PCI-6052E Analog Output (D/A)            |       |

| PXI/PCI-6052E Digital Input                  |       |

| PXI/PCI-6052E Digital Output                 |       |

| PXI/PCI-6052E Pulse Generation               |       |

| PXI/PCI-6052E Pulsa Width/Pariod Massurament |       |

| PCI-6070E (Formerly PCI-MIO-16E-1)          | . 22-89 |

|---------------------------------------------|---------|

| PCI-6070E Analog Input (A/D)                |         |

| PCI-6070E Analog Output (D/A)               | . 22-92 |

| PCI-6070E Digital Input                     | . 22-94 |

| PCI-6070E Digital Output                    |         |

| PCI-6070E Pulse Generation                  | . 22-96 |

| PCI-6070E Pulse Width/Period Measurement    | . 22-97 |

| PCI-6071E                                   | . 22-99 |

| PCI-6071E Analog Input (A/D)                | 22-100  |

| PCI-6071E Analog Output (D/A)               | 22-102  |

| PCI-6071E Digital Input                     | 22-104  |

| PCI-6071E Digital Output                    | 22-105  |

| PCI-6071E Pulse Generation                  | 22-106  |

| PCI-6071E Pulse Width/Period Measurement    | 22-107  |

| PCI-6503                                    | 22-109  |

| PCI-6503 Digital Input                      | 22-109  |

| PCI-6503 Digital Output                     |         |

| PCI-6527                                    | 22-113  |

| PCI-6527 Digital Input                      | 22-113  |

| PCI-6527 Digital Output                     | 22-115  |

| PCI-6601                                    | 22-117  |

| PCI-6601 Digital Input                      | 22-117  |

| PCI-6601 Digital Output                     | 22-118  |

| PCI-6601 Incremental Encoder                | 22-120  |

| PCI-6601 Pulse Generation                   | 22-121  |

| PCI-6601 Pulse Width/Period Measurement     | 22-122  |

| PCI-6601 Armed Pulse Generation             | 22-124  |

| PCI/PXI-6602                                | 22-125  |

| PCI/PXI-6602 Digital Input                  |         |

| PCI/PXI-6602 Digital Output                 |         |

| PCI/PXI-6602 Incremental Encoder            | 22-128  |

| PCI/PXI-6602 Pulse Generation               | 22-129  |

| PCI/PXI-6602 Pulse Width/Period Measurement | 22-130  |

| PCI/PXI-6602 Armed Pulse Generation         | 22-132  |

| PCI-6703                                 | 22-134        |

|------------------------------------------|---------------|

| PCI-6703 Analog Output (D/A)             | 22-134        |

|                                          |               |

| PCI-6704                                 | 22-136        |

| PCI-6704 Analog Output (D/A)             | 22-136        |

|                                          |               |

| PCI-6711                                 | 22-138        |

| PCI-6711 Analog Output (D/A)             | <b>22-138</b> |

| PCI-6711 Digital Input                   | 22-140        |

| PCI-6711 Digital Output                  | 22-141        |

| DOLDAY OF A                              |               |

| PCI/PXI-6713                             |               |

| PCI/PXI-6713 Analog Output (D/A)         |               |

| PCI/PXI-6713 Digital Input               |               |

| PCI/PXI-6713 Digital Output              | 22-146        |

| PCI-DIO-96                               | 22-148        |

| PCI-DIO-96 Digital Input                 |               |

| PCI-DIO-96 Digital Output                |               |

| 1 CI DIO VV Digital Output               | 110           |

| PXI-6040E                                | 22-152        |

| PXI-6040E Analog Input (A/D)             | 22-153        |

| PXI-6040E Analog Output (D/A)            |               |

| PXI-6040E Digital Input                  |               |

| PXI-6040E Digital Output                 |               |

| PXI-6040E Pulse Generation               |               |

| PXI-6040E Pulse Width/Period Measurement |               |

|                                          |               |

| PXI-6070E                                |               |

| PXI-6070E Analog Input (A/D)             | 22-162        |

| PXI-6070E Analog Output (D/A)            |               |

| PXI-6070E Digital Input                  | 22-166        |

| PXI-6070E Digital Output                 | 22-167        |

| PXI-6070E Pulse Generation               | 22-169        |

| PXI-6070F Pulse Width/Period Measurement | 22-169        |

| PX                                                 | l-6071E                                                                                          |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |          |      |     |      |                                                   |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|------|-----|------|---------------------------------------------------|